S5P4418 — это система на кристалле (SoC), основанная на 32-разрядном RISC-процессоре для планшетов и сотовых телефонов.

S5P4418 — это система на кристалле (SoC), основанная на 32-разрядном RISC-процессоре для планшетов и сотовых телефонов.

Возможности S5P4418, спроектированные с использованием техпроцесса 28 нм, включают:

- Четырехъядерный процессор Cortex-A9

- Наивысшую пропускную способность памяти

- Full HD-дисплей

- 1080p 60 декодирование видео и 1080p 30 аппаратное кодирование кадров

- 3D-графическое оборудование

- Высокоскоростные интерфейсы, такие как eMMC4.5 и USB 2.0

S5P4418 использует четырехъядерный процессор Cortex-A9, что на 50% производительнее, чем ядра Cortex-A8. Это обеспечивает пропускную способность 6,4 ГБ/с в операциях таких как кодирование и декодирование 1080p, 3D-графический дисплей и обработка сигнала высокого разрешения с дисплеем Full HD. Процессор поддерживает динамическое сопоставление виртуальных адресов, что помогает разработчикам программного обеспечения эффективно использовать ресурсы памяти.

S5P4418 обеспечивает лучшую производительность 3D-графики с широким спектром API, например OpenGL ES 1.1, 2.0. 3D полностью поддерживает Full HD-дисплей. Функция двойной дисплей поддерживает FullHD разрешение основного ЖК-дисплея и 1080p 60 кадров HDTV-дисплей по HDMI, одновременно.

Отдельный постпроцессорный конвейер позволяет S5P4418 создавать реальный сценарий отображения.

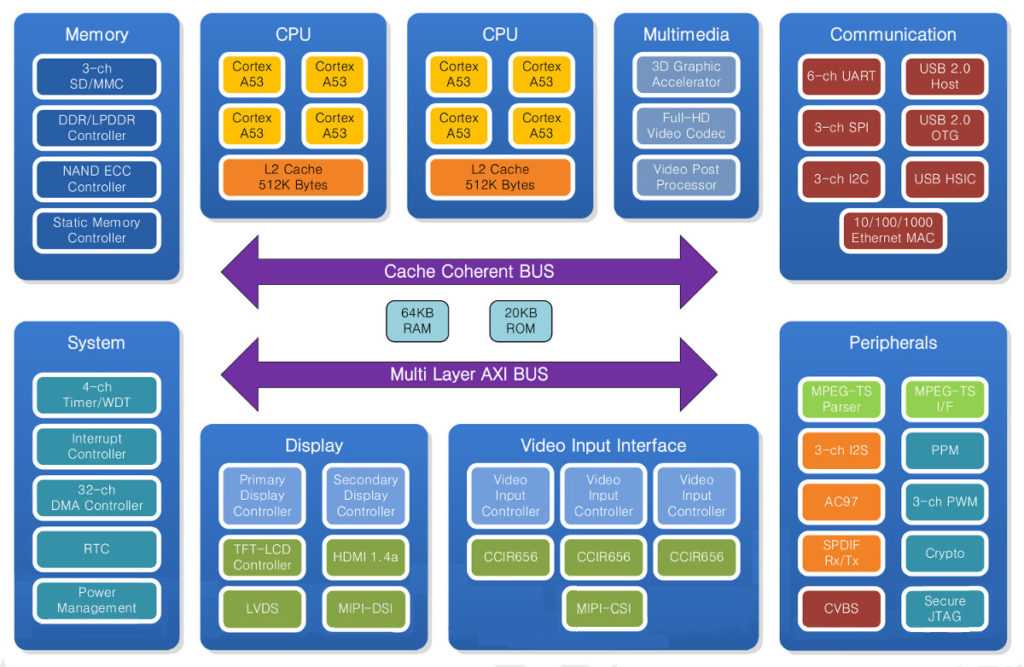

- Блок-схема

- Особенности

- Краткая функциональная спецификация

- CPU

- Управление питанием

- DMA

- Контроллер прерываний

- Таймер и сторожевой таймер

- RTC

- Контроллер памяти

- Контроллер GPIO

- Контроллер Ethernet MAC

- Контроллер SD/MMC

- PPM

- ШИМ

- АЦП

- I2C

- SPI/SSP

- MPEG-TS

- Интерфейс SIM-карты UART и ISO7816

- USB

- I2S

- AC97

- SPDIF Tx, Rx

- Контроллер дисплея

- Интерфейс LVDS

- Видеопроцессор

- Процессор видеовхода

- 3D-графический контроллер

- IP-адрес безопасности

- Условия эксплуатации

- Техническая документация (Datasheet)

Блок-схема

Особенности

28 нм техпроцесс HKMG (High-K Metal Gate)

513-контактный FCBGA, 0,65 мм Ball Pitch, размер корпуса 17х17 мм

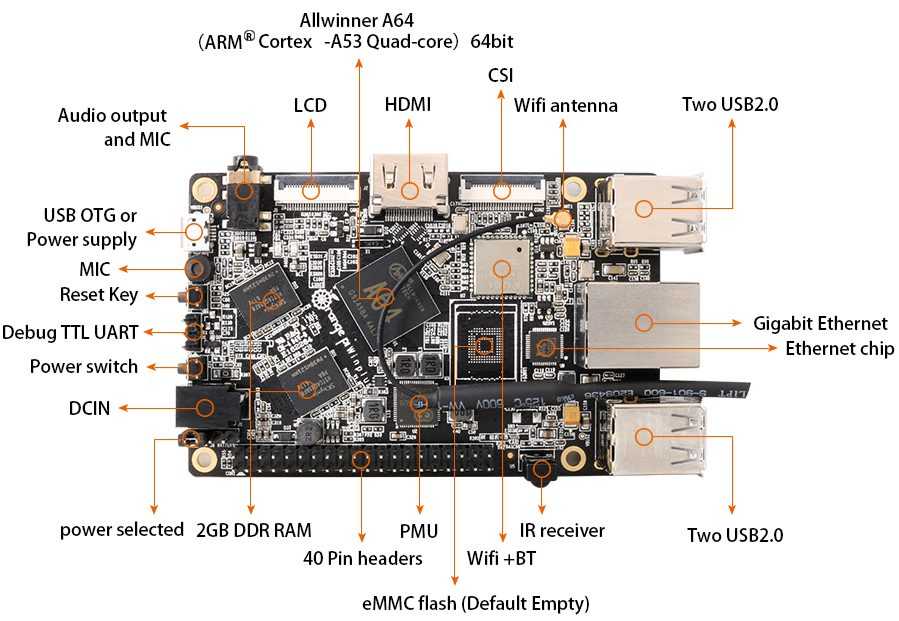

Четырехъядерный Cortex-A9 CPU

Высокопроизводительный 3D-графический ускоритель

Многоформатный видеокодек Full-HD

Поддерживает различную память: x32 LPDDR2/3, LVDDR3 (низковольтная DDR3), DDR3 до 800 МГц

Поддержка MLC/SLC NAND Flash с алгоритмом Hardwired ECC (4/8/12/16/24/40/60 бит)

Поддерживает двойной дисплей до 2048×1280, TFT-LCD, LVDS, HDMI 1.4a, выход MIPI-DSI

Поддержка 3-канального параллельного видеоинтерфейса ITUR.BT 656 и MIPI-CSI

Поддерживает 10/100/1000 Мбит Ethernet MAC

Поддерживает 3ch SD/MMC, 5ch UART, 32ch DMA, 4ch Timer, Контроллер прерываний, RTC

Поддерживает 3ch I2S, SPDIF Rx/Tx, 3ch I2C, 3ch SPI, 8ch 12-разрядный ADC, 3ch PWM и GPIO, 1ch PPM

Поддержка MPEG-TS Последовательного/Параллельногоинтерфейса и MPEG-TS HW Parser

Поддержка 1ch USB 2.0 Host, 1ch USB 2.0 OTG, 1ch USB HSIC Host

Поддерживает функции безопасности (AES, DES/TDES, SHA-1, MD5 и PRNG) и Secure JTAG

Поддерживает различные режимы питания (Normal, Sleep, Deep-Sleep, Stop)

Поддерживает различные режимы загрузки, включая NAND (с обнаружением и коррекцией ECC), SPI Flash/EEPROM, NOR, USB и UART.

Краткая функциональная спецификация

CPU

Cortex-A9 Quad Core

Кэш L1-32 Кбайт I-Cache, 32 Кбайт D-Cache

Кэш L2-1 Мбайт общего кэша

Co-Processor-VFP (векторный процессор с плавающей точкой), Neon Processor

Управление питанием

4 Spread-Spectrum PLLs

Внешние кварцевые генераторы: 24 МГц (для PLL), 32,768 кГц (для RTC)

Поддержка различных режимов питания-Normal, Idle, Stop

Приостановка оперативной памяти (Sleep, Deep Sleep)

DMA

32-канальные DMA

Memory-to-Memory Transfer

Memory to IO Transfer, IO to Memory Transfer

Контроллер прерываний

Векторный контроллер прерываний

Поддерживает 64-канальные источники прерываний

Поддерживает следующие функции:

- уровни приоритета фиксированного аппаратного прерывания

- программируемые уровни приоритета прерывания

- маскирование уровня приоритета аппаратного прерывания

- программируемая маскировка уровня приоритета прерывания

Генерация IRQ и FIQ:

- генерация программного прерывания

- тестовые регистры

- исходный статус прерывания

- статус запроса прерывания

Таймер и сторожевой таймер

4-канальный таймер с таймером сторожевого таймера

Режим нормального интервала с запросом прерывания

Сигнал внутреннего сброса активируется, когда значение счетчика таймера достигает 0 (time -out)

Механизм прерывания с использованием уровня

RTC

32-разрядный счетчик

Поддержка прерывания сигнала тревоги

Контроллер памяти

Системный контроллер памяти

Поддерживает LPDDR2/LPDDR3/VDDR3 (низковольтное DDR3) / DDR3 SDRAM до 2 Гбайт

Поддерживает мощность от 1,2 В до 1,5 В

Максимальная рабочая частота: 800 МГц

Ширина шины данных: 32-разрядная

Контроллер статической памяти

Мультиплексированный адрес: до 24 бит

SRAM, ROM и NAND Flash

Всплывающее чтение / запись

Контроллер FLASH NAND

Поддержка SLC/MLC NAND Flash

Поддержка загрузки MLC NAND

Жесткий алгоритм ECC

4/8/12/16/24/40/60-бит BCH Коррекция ошибок

Контроллер GPIO

Различные режимы прерывания GPIO

Rising Edge, Falling Edge, High Level, Low Level Detection

Индивидуальное генерирование прерываний

Контроллер Ethernet MAC

Стандартное соответствие IEEE 802.3az-2010 для энергоэффективного Ethernet (EEE)

Спецификация RGMII версии 2.6 от HP/Marvell

MAC поддерживает следующие функции:

10, 100 и 1000 Мбит/с со следующими интерфейсами PHY:

Интерфейс RGMII для связи с внешним гигабитным PHY

Полнодуплексная работа:

Автоматическая передача потока IEEE 802.3x

Полудуплексная операция:

Поддержка протокола CSMA/CD

Ethernet-класс 4 MAC Test Suite — Приложение D)

Разрыв кадра и расширение кадра при полудуплексной работе 1000 Мбит/с

Преамбула и начало ввода данных кадра (SFD) в пути передачи

Удаление преамбулы и SFD на пути получения

Автоматическое формирование CRC и Pad, управляемое на основе каждого кадра

Автоматическая конфигурация Pad и CRC для приемных кадров

До 31 48-битная проверка сравнения адресов SA с масками для каждого байта

64-битный, 128-битный или 256-битный хэш-фильтр (необязательно) для многоадресных и одноадресных (DA) адресов

Возможность передачи всех многоадресных адресных фреймов

Промежуточный режим для передачи всех кадров без фильтрации для сетевого мониторинга

Программируемая длина кадра для поддержки стандартных или Jumbo-Ethernet фреймов размером до 16 КБ

Программируемый межкадровый зазор (IFG) (40-96 бит раз с шагом 8)

Возможность передачи кадров с уменьшенным размером преамбулы

Отдельный 32-разрядный статус для пакетов передачи и приема

Обнаружение тегов VLAN IEEE 802.1Q для приемных кадров

Дополнительная фильтрация кадров:

VLAN-тег: идеальное совпадение и фильтрация на основе хэша (опция)

Уровень 3 и уровень 4: TCP или UDP через IPv4 или IPv6

Отдельные интерфейсы передачи, приема и управления к приложению

Мастер-интерфейс MDIO (опционально) для настройки и управления устройством PHY

Стандарт IEEE 802.3az-2010 для энергоэффективного Ethernet

Замена CRC, вставка или замена поля исходного адреса

Контроллер SD/MMC

3 независимых контроллера SD/MMC и портов

Защищенная цифровая память (SD mem — версия 3.0)

Secure Digital I/O (SDIO — версия 3.0)

Архитектура передового транспорта потребительской электроники (CE-ATA — версия 1.1)

Мультимедийные карты (MMC — версия 4.41, eMMC 4.5)

Поддерживает функции MMC4.41

Поддержка функций eMMC4.5

Поддержка тактовой частоты до 50 МГц

Поддержка передачи данных PIO и DMA

Поддержка ширины шины данных 1/4-бит

Наложение сигналов SPI на одни и те же GIO от контроллера SSP/SPI

PPM

Измерение периода импульса для ИК-приемника

ШИМ

3-канальный PWM-контроллер

Пять 32-битных таймеров

Программируемая логика для отдельных каналов ШИМ

Четыре независимых канала ШИМ с программируемым контролем и полярностью

Статическая конфигурация: PWM остановлен

Динамическая конфигурация: PWM запущен

Поддерживает режим автоматического перезапуска и режим однократного импульсного режима

Поддержка двух внешних входов для запуска PWM

Поддержка DMA-трансферов

Дополнительное генерирование прерываний импульсов или уровней

ШИМ имеет два режима работы:

Режим автоматического перезапуска

Непрерывные импульсы ШИМ генерируются на основе запрограммированного рабочего цикла и полярности

Импульсный режим с одним импульсом

Только один импульс ШИМ генерируется на основе запрограммированного рабочего цикла и полярности

АЦП

8-канальный аналоговый входной порт

Поддерживает следующие функции

Разрешение: 12 бит

Коэффициент конверсии: 1 MSPS

Диапазон ввода: от 0 до AVDD18

Входная частота: до 100 кГц

Цифровой выход: уровень CMOS (от 0 до AVDD10)

I2C

3-канальный контроллер шины I2C

Каждое устройство, подключенное к шине, адресуется программным обеспечением по уникальному адресу и главному/подчиненному устройству

может работать как ведущий-передатчик или как приемник

Последовательная, 8-битная ориентированная двунаправленная передача данных может производиться со скоростью до 100 кбит/с в стандартном режиме, вплоть до 400 кбит/с в быстром режиме

Количество ИС, которые могут быть подключены к одной шине, ограничено только максимальной емкостью шины 400 пФ

Повторная функция START и раннего завершения не поддерживает

Высокоскоростной режим, комбинированный формат, 10-битный адрес не поддерживаются

SPI/SSP

3-канальный контроллер SPI

Главный или ведомый режим.

Программируемая тактовая частота и предварительная шкала.

Отдельные передающие и принимаемые буферы памяти

Программируемый выбор интерфейса, синхронный последовательный порт SPI, Microwire или TI.

Протокол SPI, протокол SSP, протокол Microwire

Обслуживание запроса DMA для FIFO передачи и приема

Максимальная частота SSP CLKGEN составляет 100 МГц

Главный режим: 50 МГц (данные приема 20 МГц)

Режим ведомого: 8 МГц

MPEG-TS

Поддержка последовательного и параллельного интерфейса MPEG-TS

Поддержка аппаратного MPEG2-TS для IPTV

Интерфейс SIM-карты UART и ISO7816

5-канальный контроллер UART

Программируемое использование входа/выхода UART или IrDA SIR.

Программируемый генератор скорости передачи.

Стандартные биты асинхронной связи

Поддержка прямого доступа к памяти (DMA).

Обнаружение разрыва линии.

Поддержка функций управления модемом CTS, DCD, DSR, RTS, DTR и RI.

Программируемое аппаратное управление потоком.

Полностью программируемые характеристики последовательного интерфейса:

данные могут быть 5, 6, 7 или 8 бит

Блок IrDA SIR ENDEC, обеспечивающий:

программируемое использование входа/выхода IrDA SIR или UART

поддержка функций IrDA SIR ENDEC для скорости передачи данных до полудуплексной передачи до 115200 бит/с

поддержка нормальных бит 3/16 и малой мощности (1,41-2,23 с)

USB

1-ch USB 2.0 Host и 1-ch USB2.0 HSIC Host

полностью соответствует спецификации универсальной последовательной шины, версии 1.1, расширенному контроллеру хоста

Спецификация интерфейса для универсальной последовательной шины, версия 2.0 и openHCI: Open Host Controller

Спецификация интерфейса для USB, версия 1.0a. Контроллер поддерживает высокоскоростную передачу данных с пропускной способностью 480 Мбит/с (В 40 раз быстрее, чем режим USB 1.1) с использованием хост-контроллера EHCI, а также полной и низкой скорости через один или несколько встроенных хост-контроллеров OHCI.

На физическом интерфейсе USB 2.0 контроллер обеспечивает следующее:

UTMI: UTMI + уровень 3, версия 1.0

Высокоскоростной Inter-Chip (HSIC), версия 1.0

Поддерживает операции ping и split

Часы UTMI / UTMI + PHY поддерживают 30-МГц работу для 16-битного интерфейса или 60-МГц для 8-битного интерфейса

1-канальный контроллер USB 2.0 OTG поддерживает функции как устройства, так и хост-функции и полностью соответствует дополнению On-The-Go к USB 2.0, версия 1.3a и версия 2.0.

Соответствует дополнению On-The-Go к спецификации USB 2.0 (версия 1.3)

Соответствует стандарту On-The-Go для спецификации USB 2.0 (версия 2.0)

Программное обеспечение, настраиваемое для режимов OTG1.3 и OTG2.0

Поддержка следующих скоростей:

Высокоскоростной (HS, 480 Мбит/с),

Полноскоростной (FS, 12 Мбит/с)

Низкоскоростной (LS, 1,5 Мбит/с)

Поддержка множественного доступа с поддержкой режима DMA/без DMA

Поддержка нескольких интерфейсов на MAC-Phy

Поддерживает 16 двунаправленных конечных точек, включая конечную точку управления 0.

Поддерживает протокол запроса сеанса (SRP)

Поддерживает до 16 каналов хоста.

I2S

3-канальный I2S-контроллер для 5.1-канального аудиовыхода

16-битный / 24-разрядный режим ведущий и ведомый

Поддержка различных режимов интерфейса

I2S, выравнивание по левому краю, выравнивание по правому краю, режим DSP

Поддерживает режим TDM для интерфейса Digital MIC

Поддерживает SPDIF Rx / Tx

AC97

1-Ch AC97

Независимые каналы для стерео PCM In, стерео PCM Out, моно MIC IN

Операция на основе DMA

Все каналы поддерживают только 16-битные выборки

Переменная частота дискретизации Интерфейс AC97 Codec (48 кГц и ниже)

16-битный, 16 входных FIFO на канал

Поддержка только основного кодека

SPDIF Tx, Rx

SPDIF Tx

Поддерживает линейный PCM до 24 бит на образец

Поддерживает нелинейные форматы PCM, такие как AC3, MPEG1 и MPEG2

2×24-битные буферы, которые поочередно заполняются данными

SPDIF Rx

Последовательный, однонаправленный, самосинхронный интерфейс

Однопроводный односигнальный интерфейс

Контроллер дисплея

Поддержка Dual Display

Поддерживает 3 слоя, коррекцию гаммы и управление цветом (яркость, контрастность, оттенок и насыщенность)

Поддерживает различные пиксельные форматы RGB/BGR 444 555 565 888 с/без альфа-канала

разрешение до 2048 x 1280 при 60 Гц

Поддержка различных ЖК-дисплеев

Интерфейс I80, RGB, последовательный RGB, выход LVDS

Поддерживает полосы данных MIPI-DSI 4

Интерфейс HDMI

HDMI 1.4a, HDCP 1.4

Поддержка формата видео:

480p при 59,94 Гц / 60 Гц, 576p при 50 Гц

720p при 50 Гц / 59,94 Гц / 60 Гц

1080p при 50 Гц / 59,94 Гц / 60 Гц

Первичные трехмерные видеоформаты

Другие различные форматы до 148 МГц пикселей

Поддерживает цвет Формат: 4: 4: 4 RGB / YCbCr, 4: 2: 2 YCbCr

Поддерживает цвет: 8 бит, 10 бит, 12 бит (ПРИМЕЧАНИЕ: 16-бит не поддерживается)

Поддерживает: линейные PCM, нелинейные PCM и высокоскоростные аудиоформаты (пакеты Audio Sample и HBR пакеты для передачи звука)

Встроенный механизм шифрования HDCP для защиты видео/аудио контента (процедура аутентификации управляемый S/W, а не H/W)

Интерфейс SPDIF и интерфейс I2S для аудиовхода

Поддержка функции AES KEY Decryption для внешнего управления ключами HDCP

Интерфейс LVDS

Диапазон выходных тактов: от 30 до 90 МГц

35: 7 сжатие данных до 630 Мбит/с на каждом канале LVDS

Режим отключения питания

Ширина полосы пропускания до 393,75 Мбайт/с

6 выходных каналов LVDS (5 каналов данных, 1 тактовый канал)

MIPI-DSI Соответствует стандартной спецификации MIPI DSI V1.01r11

Максимальное разрешение до WUXGA (1920 x 1200)

Поддерживает 1, 2, 3 или 4 полосы данных

Поддерживает формат пикселей: 16 бит/с, 18 бит/с, 1бит/с, слабо упакованы (3 байтовый формат) и 24 бит/с

Соответствует протоколу с протоколом PHY (PPI) в формате 1,5 Гбит/с MIPI D-PHY

Поддержка интерфейса RGB для входа видеоизображения с контроллера дисплея

Поддержка интерфейса I80

Поддерживает интерфейс управления PMS для PLL

Поддерживает Prescaler

Видеопроцессор

3D-контроллер чересстрочной развертки

Fine Scalar для видео

Процессор видеовхода

Максимальная поддержка разрешения 8192 x 8192

Supports 8-бит формат BT656, 601

Поддерживает MIPI-CSI

Поддержка первичного и вторичного изображений

— YUV420, YUV420 (Legacy), YUV420 (CSPS), YUV422 из 8 бит и 10 бит

— RGB565, RGB666, RGB888

— RAW6, RAW7, RAW8, RAW10, RAW12, RAW14

— формат сжатия: 10-6-10, 10-7-10, 10-8-10

Совместимость с PPI (интерфейс Protocol-to-PHY) в спецификации MIPI D-PHY

Поддержка 4-канального виртуального канала или чередования данных

Соответствует стандарту MIPI CSI2 V1.01r06

Стандартная спецификация D-phy V1.0

3D-графический контроллер

Поддерживает OpenGL | ES 1.0 и 2.0

Поддержка OpenVG 1.1

GPU — аппаратный ускоритель для 2D и 3D графических систем.

Графический процессор состоит из:

от одного до четырех пиксельных процессоров (PP)

геометрический процессор (GP)

контроллер кэша уровня 2 (L2)

блок управления памятью (MMU) для каждого GP и PP, включенных в GPU

блок управления питанием (PMU).

Полное сглаживание сцены (FSAA).

Функции процессора геометрии:

программируемый вершинный шейдер

гибкие форматы ввода и вывода

генерация списков автономных операций

индексированный и неиндексированный ввод геометрии

IP-адрес безопасности

Встроенное защищенное загрузочное ПЗУ / ОЗУ

Аппаратное ускоритель Crypto

DES / TDES, AES, SHA-1, MD5 и PRNG

Поддержка Secure JTAG

Условия эксплуатации

Рабочее напряжение

Ядро: 1,0 В

Процессор: от 1,0 В до 1,3 В

Память DDR: от 1,2 до 1,5 В

I/O: 3,3 В

Техническая документация (Datasheet)

|